## New control scheme for a dynamic voltage restorer based on selective harmonic injection technique with repetitive controller

Pawan C. Tapre<sup>1</sup>, Mohan P. Thakre<sup>2</sup>, Ramesh S. Pawase<sup>3</sup>, Jaywant S. Thorat<sup>4</sup>, Dipak J. Dahigaonkar<sup>5</sup>,

Rahul G. Mapari<sup>6</sup>, Sunil Somnath Kadlag<sup>3</sup>, Shridhar Khule<sup>7</sup>

<sup>1</sup>Department of Electrical Engineering, SND College of Engineering and Research Center, Yeola, India

<sup>2</sup>Department of Electrical Engineering, SVERI's College of Engineering, Solapur, India

<sup>3</sup>Department of Electronics and Telecommunication Engineering, Amrutvahini College of Engineering, Sangamner, India

<sup>4</sup>Department of Research and Development, Vision Vidyalaya Engineers Private Limited, Thane, India

<sup>5</sup>Department of Electronics and Communication Engineering, Shri Ramdeobaba College of Engineering and Management, Nagpur, India

<sup>6</sup>Department of Electronics and Telecommunication Engineering, Pimpri Chinchwad College of Engineering and Research, Pune, India

<sup>7</sup>Department of Electrical Engineering, Matoshri College of Engineering and Research Center, Nashik, India

---

### Article Info

#### Article history:

Received Nov 21, 2022

Revised Feb 23, 2023

Accepted Mar 8, 2023

---

### ABSTRACT

Repetitive controller and selective harmonic injection technique (SHI) in medium and low voltage distribution networks improve dynamic voltage restorer (DVR) DC bus voltages as well as nullify power quality (PQ) problems. DVRs use sinusoidal pulse width modulation (SPWM) firing control, but DC bus use seems to be limited, affecting density, cost, and power packaging. By adding 1/6<sup>th</sup> of the 3<sup>rd</sup> harmonic waveform to the basic waveform, SPWM yields the developed model. According to the findings, 15% of DC bus usage improves and produces high voltage AC. Nevertheless, just control systems perturb PQ. The proposed controller uses feed forward and feedback to enhance transient response and justify stable zero error. 3<sup>rd</sup> third harmonic injection pulse width modulation (THIPWM) improves total harmonic distortion (THD) in the proposed scheme. Power system computer aided design (PSCAD) simulation produced high accuracy for THIPWM and repetitive controllers.

*This is an open access article under the [CC BY-SA](#) license.*

---

### Corresponding Author:

Mohan P. Thakre

Department of Electrical Engineering, SVERI's College of Engineering

Solapur, India

Email: mohanthakre@gmail.com

---

## 1. INTRODUCTION

The quality of electrical power and disruptions in the power signal has become serious problem among electrical power suppliers and customers. Continuous monitoring of power is intended to enhance the power quality (PQ) which is delivered at the customer's site. Thus further, it is highly desirable to detect PQ disturbances (PQD) and a proper description of PQD [1]–[3]. Two somewhat distinct characteristics of all PQ issues are present such as energy and total harmonic distortion [4], [5]. The PQD is recognized to regularly the  $V_{sag}$  due to a switch on abnormal conditions in the network [6], [7].  $V_{swell}$  is less common in distribution networks owed to switch on capacitive load. Harmonics due to non linear loads like furnaces and electronic devices [8], [9]. This PQD causes process shutdown which leads to financial loss. Various conventional methods are used to reduce the  $V_{sag}$  but by far the most effective approach is FACTS devices [1], [10]. Dynamic voltage restorer (DVR), distributed static compensator (DSTATCOM), static synchronous compensator (STATCOM), synchronous series compensator (SSSC), and static VAR compensator (SVC) are the flexible alternating current transmission systems (FACTS) devices that are increasingly being used to

minimize  $V_{sag}$  and other PQD [10]–[14]. The important continuation of this paper is to use repetitive controllers to formulate a governing arrangement for DVR and mitigate PQ problems. Besides that, the authored DVR customs device has been facilitated by a proportional integral (PI) controller which substitutes network voltage frequency [15], [16]. An uncomplicated mechanism is adequate to allow the reduction of voltage and to compensate for those fairly unbalanced voltages. Still, when traded with a high concert application it flops therefore, intricate controllers added are compulsory [17].

According to Nielsen *et al.* [18], the limitation of such a method is that it requires a completely autonomous filter that diminishes the independent harmonic [7]. Feed forward +PI controller feedback has been used [16] to restore the regulate global concert while being aware of a variant of the  $t_0$  measured strategy in addition to the filter output constraint. As it can alleviate all 4 abnormalities, the framework becomes relatively simple as well as adaptable [17]. It consists of a feed forward cycle to increase the transient state and a feedback cycle to enable zero error. It could simply be done unbiasedly with such a  $t_0$  in digital signal processing [18], [19]. In recent decades, research in  $V_{sag}$  assessment might have concentrated on creating protocols as well as methods for evaluating the disturbance [20]–[22]. There has been very little research into the causes of  $V_{sag}$ . For the remediation of PQ problems, numerous pulse width modulation (PWM) methods have been employed in DVR [23], [24]. In the existing crisis, analysts have been employing the selective harmonic elimination pulse width modulation (SHEPWM) and space vector pulse width modulation (SVPWM) strategy for DVR [25]–[27]. Even so, no dependable and technically proficient technique of implementation in an effective way is available at this time. In the sinusoidal pulse width modulation (SPWM), limited accessible voltage has been found, which would be critical for cost and power compactness excellence [28]. This will primarily address the vital third harmonic injection (THI) and it will be better to implement. The resulting flattened upper surface output signal tolerates completed modulation while retaining an estimable harmonic band [29]–[31].

In this article following points have been discussed. Section 2 describes the DVR framework and repetitive controller, in section 3 a DVR with SPWM repetitive control technique is employed. In section 4 the third harmonic injection pulse width modulation (THIPWM) DVR methodologies are intentional. Considered in designing to simulate the repetitive controller along with the parameters for information are provided in sections 5 and 6 performance with proposed control strategy with conclusion explained.

## 2. DYNAMIC VOLTAGE RESTORER AND REPETITIVE CONTROLLER

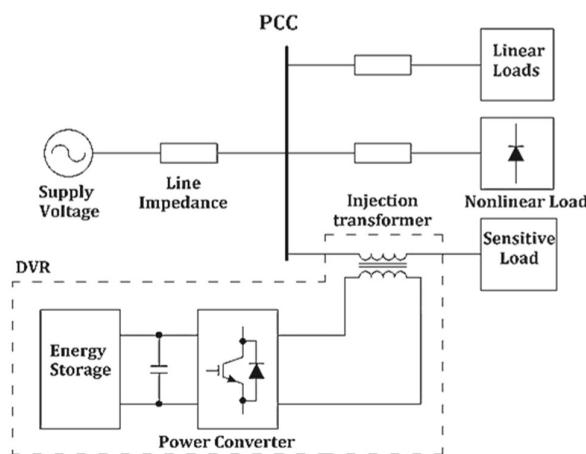

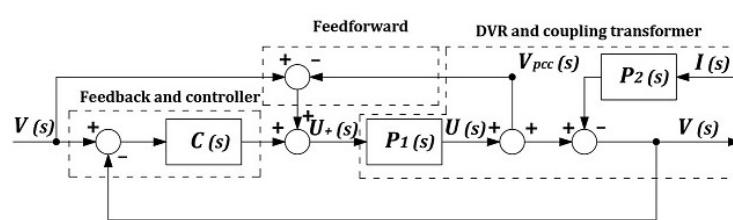

The system configuration includes a DVR control circuit and power circuit shown in Figure 1 a perceptive load, which includes linear and non-linear loads is added to the system. The DVR has so far been mainly comprised of a voltage sourced converter (VSC) hooked up to the AC configuration through a voltage transformer (VT), with said contact network presented in Figure 1 among supply and differentiated loads. Figure 2 seems to be simply a reflection of the respective circuit depicted in Figure 1. In which acronyms details are given in the nomenclature part. Perceptive load voltage as (1):

$$v(t) = V_{pcc}(t) + u(t) - Ri(t) - L \frac{di}{dt} \quad (1)$$

Figure 1. Basic block diagram of DVR with various loads

Figure 2. Equivalent DVR circuit with perceptive load [6]

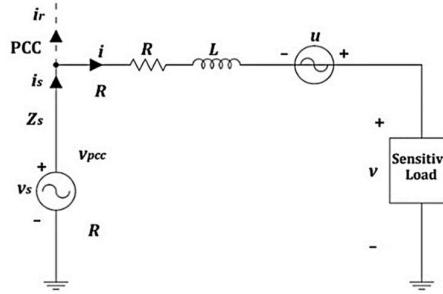

Once periodic signals must be accompanied or denied, an resistor capacitor (RC) is an attempt to control way is to ensure in the internal model theory (IMP). A generic periodic signal with the ability to IMP seems to have the aforementioned shape. Figure 3 depicts a basic repetitive controller reorientation. The primary goal of a repetitive controller would be to verify that the reference of periodic trajectories has been monitored or that repeated disruptions are denied in a continuous system [29], [30].

Figure 3. Repetitive controller reorientation [27]

### 3. PROPOSED METHOD

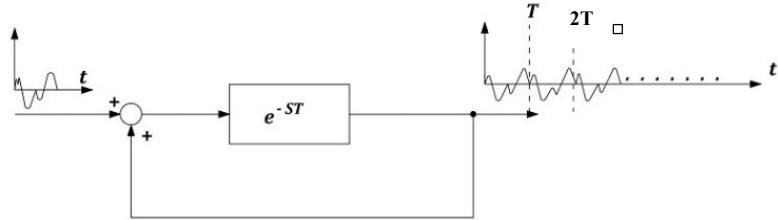

An essential duty of the DVR is to manage the  $V_{load}$  under the observation of different sorts of disruption. Throughout this article, the suggested closed loop control setup has been premised to make sure accurate results in a steady state condition. A prolonged time full closed loop DVR optimization approach is demonstrated in Figure 4.  $P_1(s)$  has been the total amount of 1 sample period and the  $t_0$  of the inverter implicated in PWM transitioning. Those philosophies should be computable, and the design should be easily enlarged for the three phase base. The output that's also adhered to the load is as tries to follow: A DVR control system,  $C(s)$ , has been as (2):

$$C(s) = \frac{M(s)}{1 - e^{-\frac{2\pi}{\omega_1}s}} \quad (2)$$

Figure 4. DVR control scheme

In which  $M(s)$  has become a favored term frequency (TF), ensuring stability. Takeover (2) [15]:

$$F(s) = \frac{\left[ 1 - e^{-\frac{2\pi}{\omega_1}s} + M(s) \right] P_1(s)}{1 - e^{-\frac{2\pi}{\omega_1}s} + M(s) P_1(s)} \quad (3)$$

$$F_w(s) = \frac{[1-P_1(s)][1-e^{-\frac{2\pi}{\omega_1}s}]}{1-e^{-\frac{2\pi}{\omega_1}s} + M(s)P_1(s)} \quad (4)$$

$$F_i(s) = -\frac{[1-e^{-\frac{2\pi}{\omega_1}s}]P_2(s)}{1-e^{-\frac{2\pi}{\omega_1}s} + M(s)P_1(s)} \quad (5)$$

The attribute would be supplanted by  $j$  when determining the frequency response from (3) to (5). To assist in resolving the origin of complexity caused by certain parts that are modeling errors, time delay, and dead time due to inverter issues. The control system (2) could be changed as (6):

$$C(s) = \frac{Q(s)e^{-(T-\hat{t}_o)s}}{1-Q(s)e^{-T}} \quad (6)$$

$Q(s)$ , pass filter TF [9];  $\hat{t}_o$  is indeed a for the DVR delay, with  $T=2\pi/\omega_1$ , as well as  $\beta$  an approach limitation that is lower than the network voltage time frame ( $\beta < (2\pi)/(\omega_1)$ ). By modifying (6) throughout [16].

$$F_w(s) = \frac{[1-e^{-t_o s}][1-Q(s)e^{-Ts}]}{1+Q(s)e^{-Ts}(e^{-\delta s}-1)} \quad (7)$$

$$F_i(s) = -\frac{[1-Q(s)e^{-Ts}]P_2(s)}{1+Q(s)e^{-Ts}(e^{-\delta s}-1)} \quad (8)$$

with,  $\delta = t_o - \hat{t}_o$ .

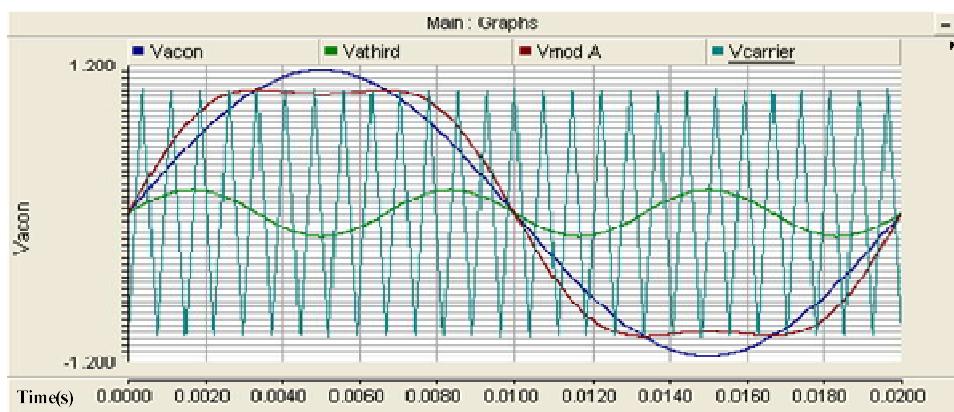

### 3.1. Third harmonic injection pulse width modulation strategy in a dynamic voltage restorer

The SPWM technique has been used for DVR in the majority of investigations. Even so, the utilization of the dc bus has been insufficient in the SPWM. The goal of such an approach becomes to enhance the  $V_{L-L}$  of a PWM inverter by 15% without the need for a pulse drop modulation scheme. Because of the incorporation of 3<sup>rd</sup>, 9<sup>th</sup>, and 15<sup>th</sup> harmonics, in which amplitudes are 1/6<sup>th</sup> and 3<sup>rd</sup> harmonics decided to add to the sinusoidal waveform [29], [30]. Such harmonics feed on the ground toped phase waveform, which improves inverter effectiveness, but castoffs have been castoffs in today's high scheme and have been initiated in this technique, which concentrates on IGBT DVR. The 3<sup>rd</sup> harmonic scale function is stated to be capable of making a phenomenal change to the inverter's output phase waveform given (9).

$$y = \sin \omega t + A \sin 3 \omega t \quad (9)$$

From which  $A$  is recognized as  $y$  optimal value, this could be expressed as (10).

$$\frac{dy}{dt} = \cos \omega t + 3A \cos 3 \omega t = 0 \quad (10)$$

As a result, the waveform's maxima and minima occurred at (11) and (12):

$$\cos \omega t = 0 \quad (11)$$

$$\cos \omega t = \frac{(9A-1)^{1/2}}{12A} \quad (12)$$

In (9) becomes:

$$y = (1 + 3A) \sin \omega t - 4A \sin^3 \omega t \quad (13)$$

$$y = \sin \omega t + \frac{1}{6} \sin 3 \omega t \quad (14)$$

To show that no more inclusion in by summing of triple harmonics seems to be feasible, the values of  $t$  over which mountain ranges of  $y$  occur are initiated by modifying (11) and (12). As expected, (11) yields  $\omega t = \pi/2$  independent of  $A$ , and yet (5) yields:

$$\cos \omega t = \frac{1}{2} \quad (15)$$

$$\text{i.e., } \omega t = \pi/3, \omega t = 2\pi/3 \quad (16)$$

Those triple harmonics surpass 0 throughout all  $\omega t$  statistics. Thereby, bringing triple harmonics did not affect the additional fall  $\hat{y}$ , as well as the special hypothesis, is accurate.  $\omega t = n\pi/3$  in (14), find the maximum values of  $y$ .

$$y = \pm \frac{\sqrt{3}}{2} \quad (17)$$

and,  $\hat{y} = \pm 0.866$

Essentially,  $2/3^{\text{rd}}$  is the reference sinusoidal waveform, and by including a  $3^{\text{rd}}$  harmonics aspect whose magnitude has been  $1/6^{\text{th}}$  of the original input waveform, the peak value of output has been reduced by an element of 0.866 without modifying the fundamental amplitude. One such technique has been depicted in Figure 4; a component here raises the modulating wave magnitude, allowing the inverter's absolute  $V_{\text{max}}$  to be applied once more. In addition to modulating waveform in (18):

$$y = K \left( \sin \omega t + \frac{1}{6} \sin 3 \omega t \right) \quad (18)$$

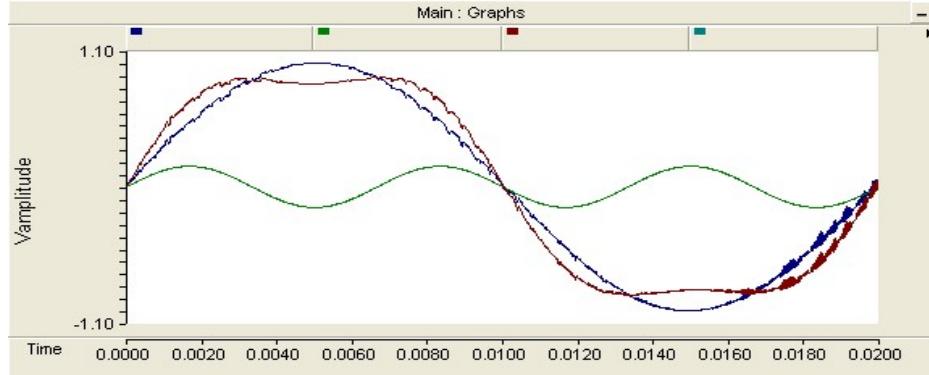

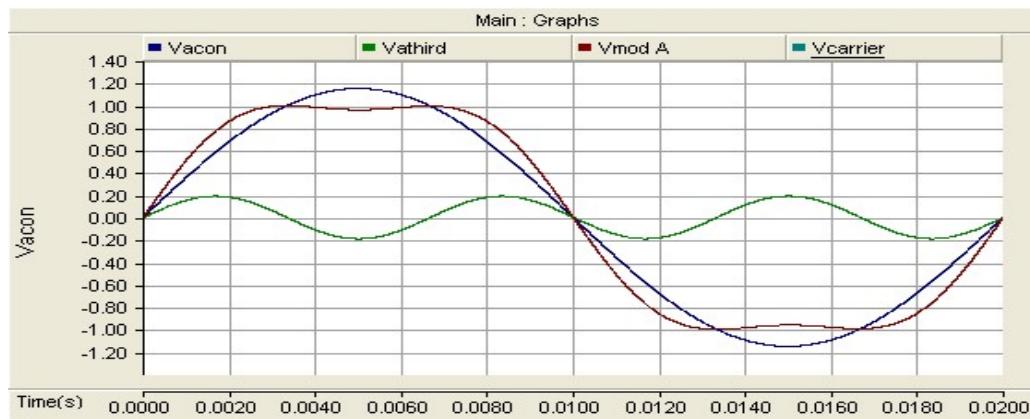

Let's assume no least pulse width threshold exists,  $y$  has been attributed to 1. According to the waveform seen in Figure 5, the maximum value of  $y=0.866$ . The sum of  $1/6^{\text{th}}$  of the  $3^{\text{rd}}$  harmonic findings in such a 15.6% rise is in the amplitude of the fundamental phase voltage waveform [31] and thus in the load voltage waveform as shown in Figure 5.

$$1 = K \times 0.866 \text{ and } K = 1/0.866 = 1.15 \quad (19)$$

Figure 5. Rising a basic  $V_o$  by  $1/6^{\text{th}}$  of the  $3^{\text{rd}}$  harmonic reference peak=0.866 and fundamental magnitude=1

#### 4. METHOD

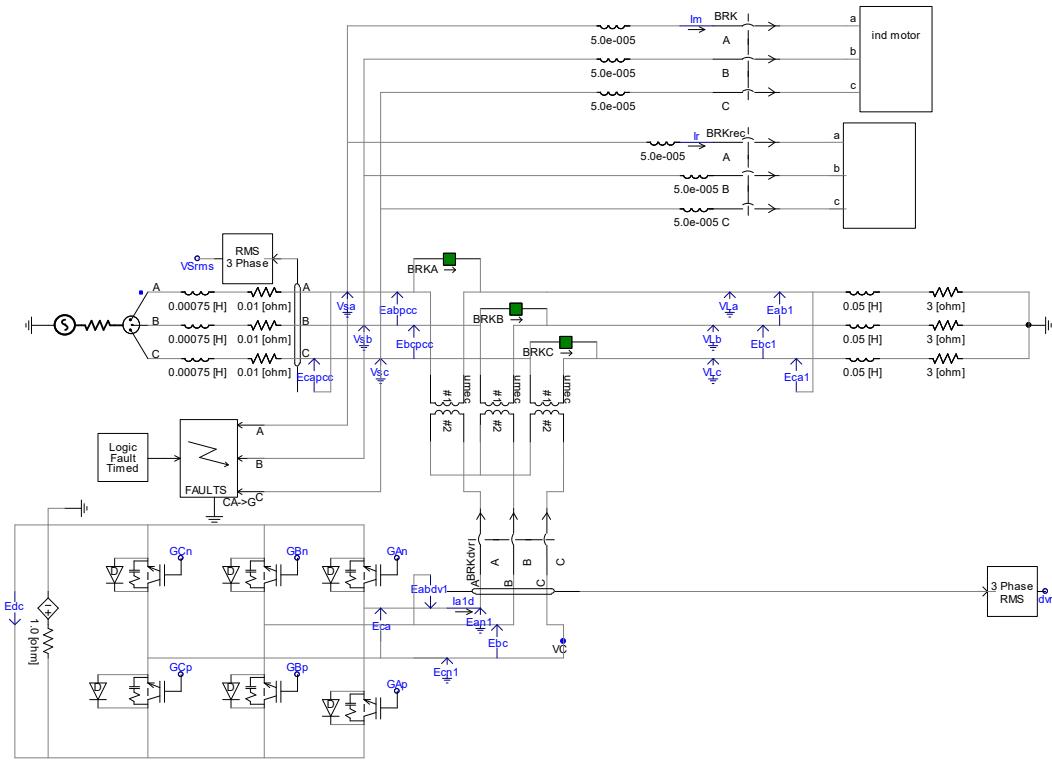

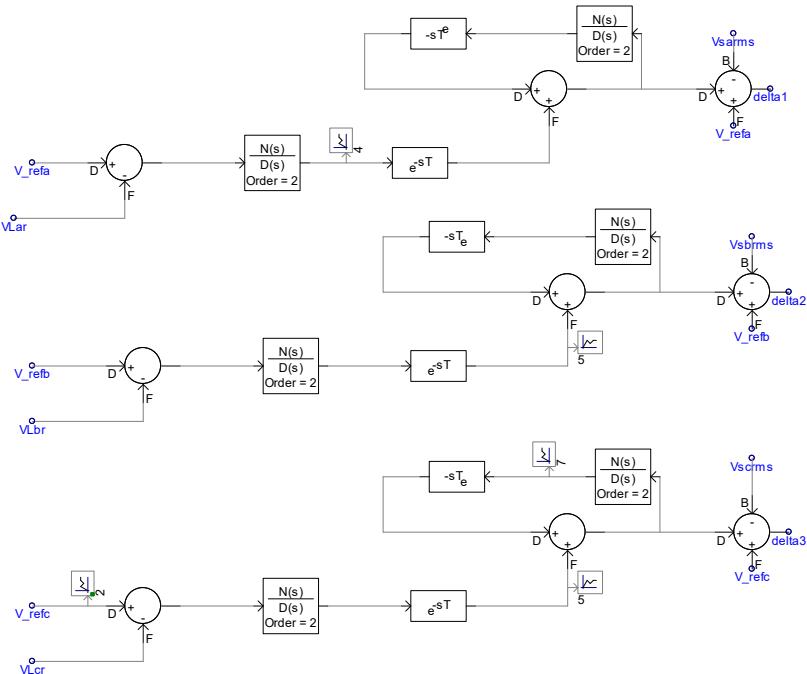

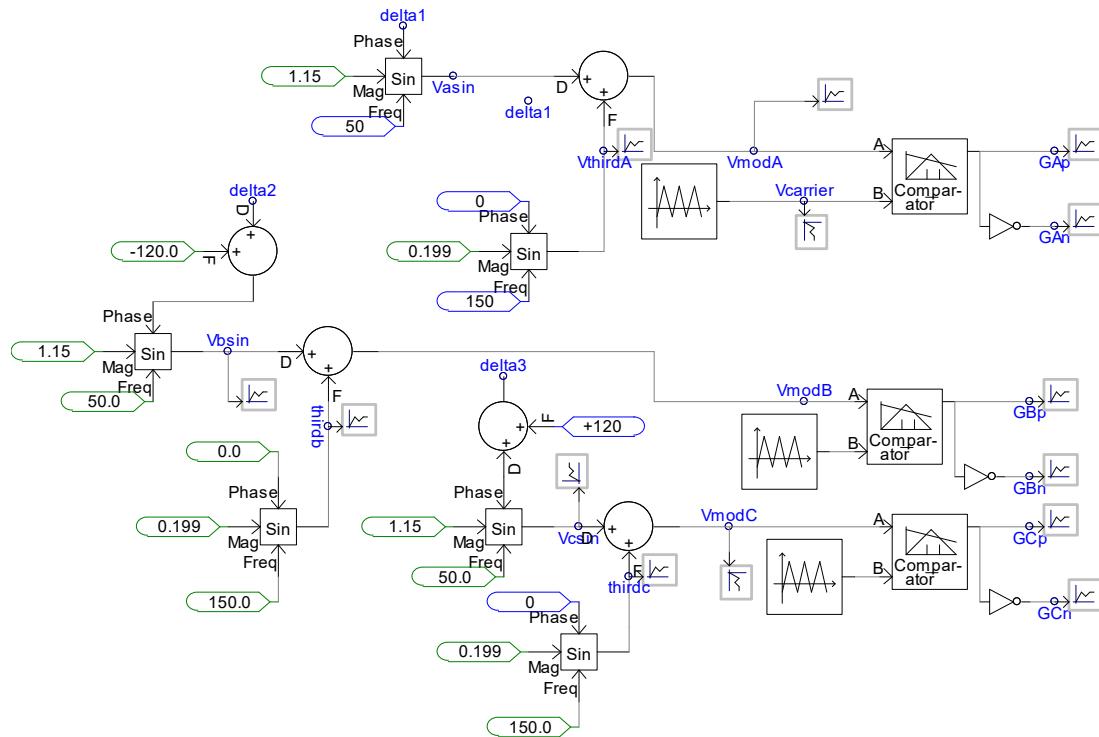

The DVR topologies with various loads shown in Figure 1 and the RC closed loop strategy of control for DVR shown in Figure 4 were simulated in power system computer aided design software, as shown in Figures 6-8 respectively. The test system consists of a 400 V, 50 Hz, three phase source feeding three separate loads i.e., induction motor, nonlinear load three phase rectifiers, and three phase perceptive rectifiers. A DVR has been linked in between point of common coupling (PCC) and the delicate load via a 20 kVA transformer with a unit turns ratio as well as a secondary coil bushed to the star. The  $V_{dc}$  storage device has been 400 V SPWM. Table 1 tabulated system parameters and controller parameters of the DVR system.

To appropriately architecture the controller attribute, a monetary value for the  $t_0$  has been chosen within a specified range [29]. The PWM has been responsible for the  $t_0$ . SPWM can be used in any subheading to generate switching pulses for the controller, being a three phase conversion. For each phase, a controller was configured using a coordinating scheme of three phases  $a$ ,  $b$ , and  $c$ . Maybe, if operating under

imbalance situations, the references frame *a*, *b*, and *c* has become the most prevalent solution to the regulation of load voltage.

Figure 6. The study system developed in simulation software

Figure 7. Repeatable controller applied in PSCAD

Figure 8. The software incorporates the THI approach for DVR

Table 1. Test system and controller parameters

| Study system parameters                    |                                                     | DVR controller parameters            |           |

|--------------------------------------------|-----------------------------------------------------|--------------------------------------|-----------|

| Parameter                                  | Value                                               | Parameter                            | Value     |

| $V_{RMS\ L-L}$                             | 5 Hz                                                | Switching frequency ( $f_s$ )        | 6.45 kHz  |

| R and L of the distribution line           | $R_s=10\text{ m}\Omega, L_s=750\text{ }\mu\text{H}$ | Frequency-modulation Index ( $m_f$ ) | 27        |

| Motor inductance                           | $L_f=50\text{ }\mu\text{H}$                         | DVR delay ( $t_0$ )                  | $1/2f_s$  |

| Resistance and inductance of the DC load   | $R_{dc}=10\text{ }\Omega, L_{dc}=0.4\text{ H}$      | $\delta$                             | $0.2 t_0$ |

| Perceptive load: resistance and inductance | $R_{sl}=3\text{ }\Omega, L_{sl}=50\text{ mH}$       | Amplitude modulation index ( $m_a$ ) | 0.8       |

## 5. RESULT AND DISCUSSION

The simulation circumstance in the discrete shown in Figure 6 where the simulation was performed is as follows. The simulations are represented as nonlinear load trails and the DVR is coupled at  $t = 0$  s, L-G fault is generated at PCC from  $t = 0.2$  s to  $t = 0.28$  s through an  $R_f = 0.3\text{ }\Omega$ .

### 5.1. Sinusoidal pulse width modulation computation with resistor capacitor

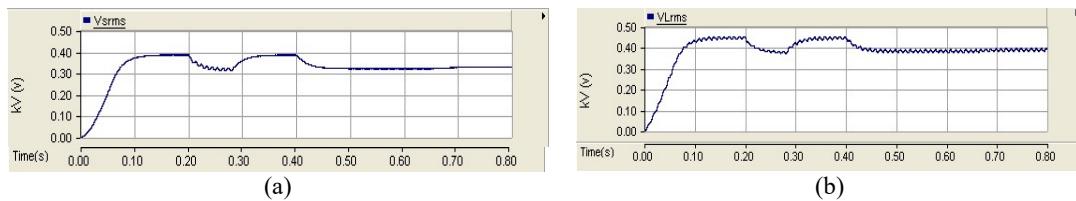

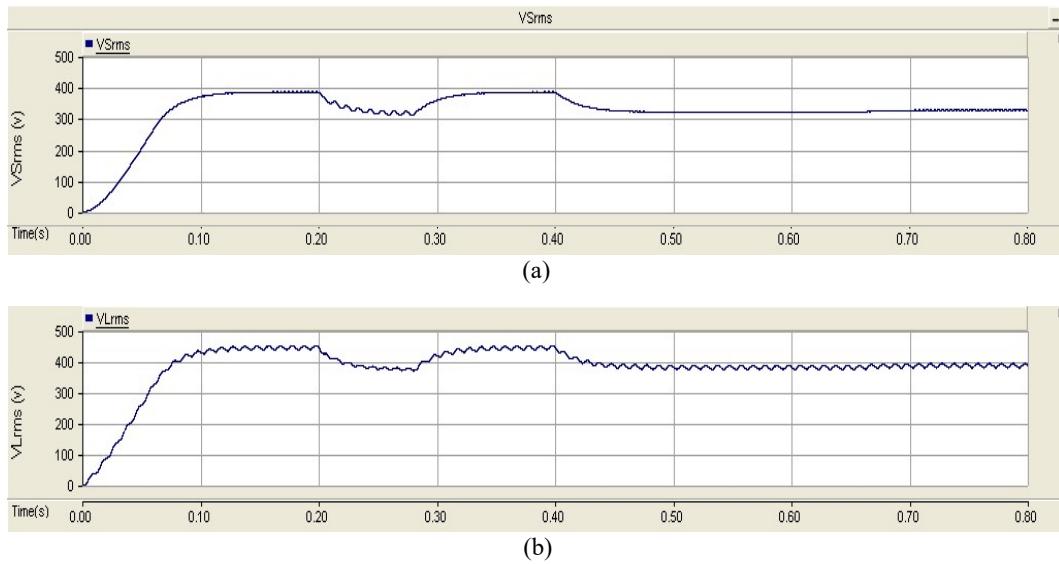

At PCC, the  $V_{RMS}$  is initially 381 V and when the  $L-L$  fault becomes practical this falls to 316 V. When the Induction drive is associated at  $t=0.4$  s, the  $V_{PCC}$  falls to 336 V trying to instigate  $V_{sag}$  by 16% w.r.t. the present value. Towards the end the nonlinear charge is isolated towards  $t=0.65$  s and at the PCC the voltage rises to 350 V. Figures 9(a) and (b) demonstrates an estimate of  $V_{LRMS}$  and  $V_{SRMS}$  that the DVR could deliver 400 V at responsive load, as well because of the various variations in voltage at PCC.

Figure 9. 3φ RMS voltage; (a)  $V_{Srms}$  at PCC without DVR and (b)  $V_{Lrms}$  at perceptive load with DVR

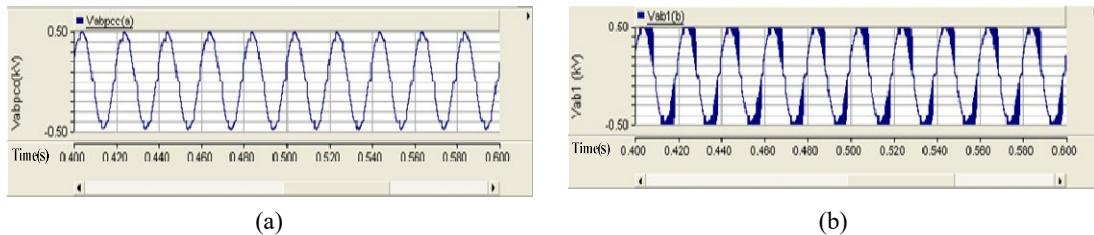

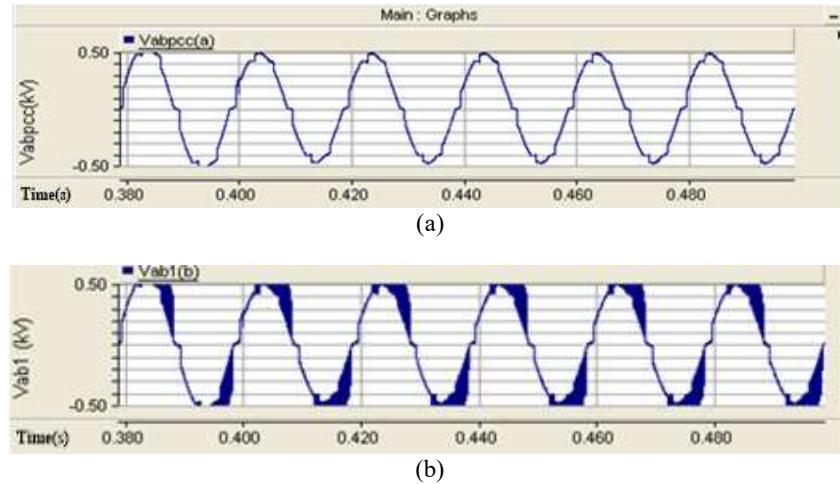

Figures 10(a) and (b) show outcomes in the case of nonlinear load and perceptive load contact alone, with an interference time of 0 to 0.2 s. Figure 10(a)  $V_{L-L}$  illustrations in the PCC  $V_{ab}P_{cc}$ , the distortion of the waveform is due to the harmonic current haggard of the rectifier, so the total current provides perceptive load and the rectifier root a drop in the PCC voltage.  $V_{L-L}$ 's fourier analysis indicates that the RMS value for the basic frequency=381 V and THDV=4.40%.

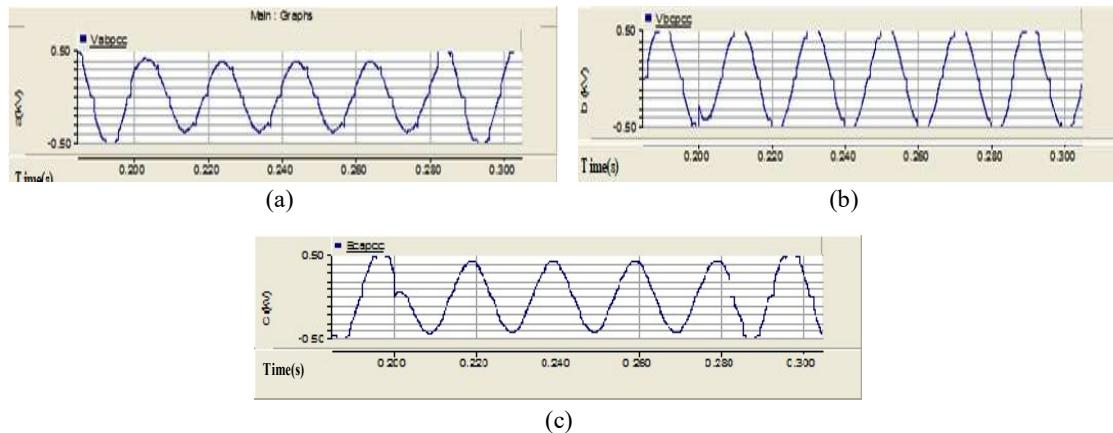

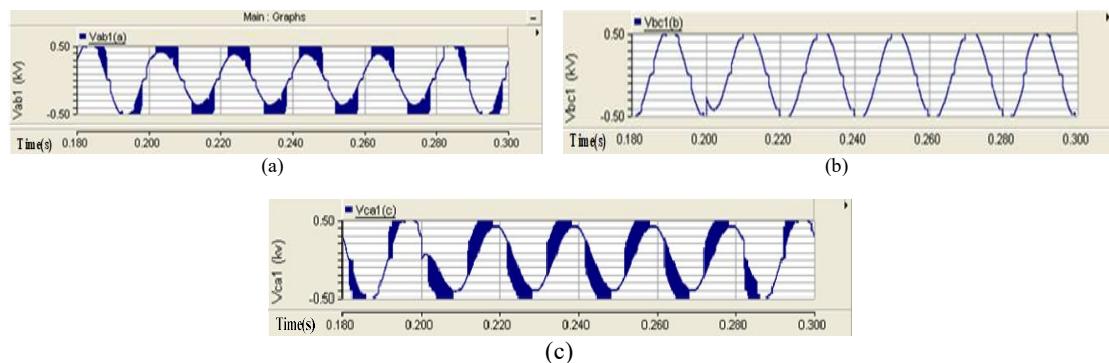

Illustrations of  $V_{L-L}$  over delicate load as described in Figure 10(b), throughout this case, the fundamental harmonic appears to have a voltage of 403 V<sub>rms</sub>, although the THD is THDV=3.27%. This harmonic distortion value was considered to be due to harmonics of high frequency that facilitate the PWM technique. The consequences gained subsequently are shown in Figures 11(a) to (c) and 12(a) to (c) of a short circuit that occurs. It is seen that  $t=0.2$  s to the given period  $t=0.28$  s from time interval. Figure 12 simply proves the fault and roots of an unbalanced  $V_{sag}$  and repetitive controller compensated voltages are shown in Figures 13(a) and (b). At the time of 0.4 s induction, the drive is started and this results in  $V_{sag}$  of 83% of normal PCC voltage this is exposed in Figure 13. The load voltage is improved to 99.5% using the repetitive controller.

Figure 10. Line voltage; (a) at PCC and (b) across perceptive loads with DVR for consistent to the interval  $0.2 \leq t \leq 0.28$

Figure 11.  $V_{L-L}$  at; (a)  $V_{PCC} AB$ , (b)  $V_{PCC} BC$ , and (c)  $V_{PCC} CA$  consistent with the interval  $0.2 \leq t \leq 0.28$

Figure 12.  $V_{L-L}$  at load; (a)  $V_{ab1}$ , (b)  $V_{bc1}$ , and (c)  $V_{ca1}$  consistent to the interval  $0.2 \leq t \leq 0.28$

Figure 13.  $V_{L-L}$ ; (a) at the PCC and (b) at the perceptive load consistent with interval  $0.4 \leq t \leq 0.65$

### 5.2. Third harmonic injection pulse width modulation computation with resistor capacitor

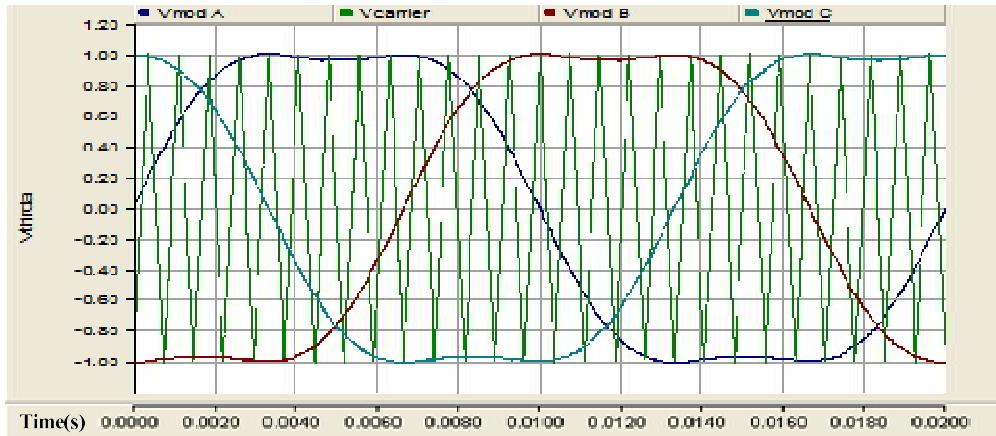

The inclusion of a 6<sup>th</sup> of a 3<sup>rd</sup> harmonic, as depicted in Figures 14 to 17, improves the magnitude of the basic  $V_{ph}$  and thus the  $V_L$  by 15.5%. Having taken marginal constraints in pulse width into account, a significant lead to an increase in  $V_o$  seems to be possible. The  $V_{L-L}$  waveform remains constant because this phase waveform nullifies the 3<sup>rd</sup> harmonic content. The  $V_{ph}$  peak of the fundamental element in SPWM is  $V_{dc}/2$  as compared to  $2 V_{dc}/2$  when controlled by 6 pulses. In the SPWM methodology, the value of the  $V_{dc}$  bus has been  $(V_{dc}/2)/(2 V_{dc}/\pi)$  in other words  $0.785=78.55\%$ .

Figure 14. 3<sup>rd</sup> harmonic added to peak reference=1 and FA=1.15

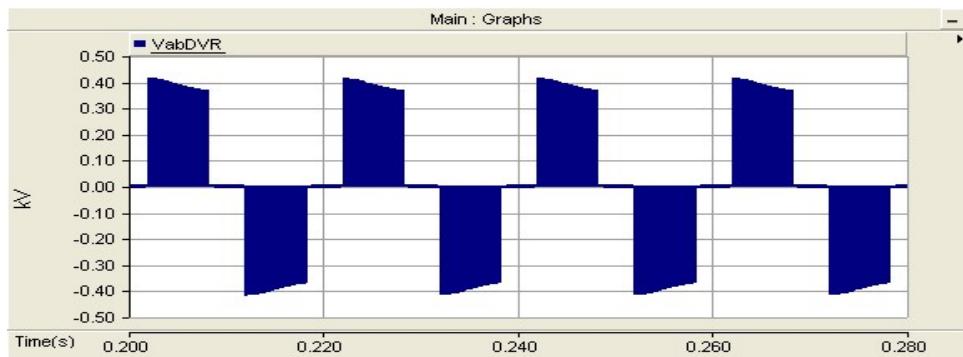

The fundamental entity's  $V_{pn}$ -Peak besides THIT is  $0.785*1.15=0.907$  (90.07%). Figure 14 illustrates waveform orientation tilted besides having to add 1/6<sup>th</sup> of the 3<sup>rd</sup> harmonic with such a 1.15 peak sine wave reinstate particularly in comparison to the amplitude of 1. Figures 15(a) and (b) show  $V_{PCCRMS}$  and  $V_{LRMS}$  with THIPWM 285 V, in which the amplitude of the foundational has been 1.15 and indeed the reference, has been recovered to 1. Figure 16 depicts the DVR-  $V_{L-L}$  with THIPWM whenever the  $V_{dc}$  bus has been set to 284 V. Once the DC bus voltage seems to be 400 V, the  $V_{pn}$ - peak using the SPWM for  $ma=0.8$  is 282 V, which is then equated with the THIPWM method.  $V_{dc}$  bus was 325 V, at that time the fundamental peak has been 282 V, and although TPIPWM has been abridged at 285 V,  $V_{dc}$  increased by 15% in contrast to SPWM as shown in Figures 17 and 18.

Figure 15. Line voltage RMS magnitude; (a) at PCC and (b) load with THIPWM when  $V_{dcbus}=285$  V

Figure 16. Line voltage of DVR supporting THIPWM ( $V_{dcbus}=284$  V)

Figure 17. For 1/6<sup>th</sup> of the 3<sup>rd</sup> added harmonic and peak reference value restored to 1 peak=1, FA=1.15 phase A

Figure 18. 3<sup>rd</sup> harmonic injected technique with a 1/6<sup>th</sup> of a 3<sup>rd</sup> harmonic applied value and a peak restored to 1, PA=1, FA=1.15

## 6. CONCLUSION

As discussed, in the THI method, the DVR performance has been improved from 77.6% to 91% in SPWM and THIPWM methods respectively in terms of the use of DC-bus. Consequently, the DVR rating is enhanced with the same rating of DVR. From the figures and findings, the THD comparison of SPWM and THIPWM it is observed that THD is down slightly. The main feature of the repetitive controller deals with PQD. Thus, based on the overall study repetitive controller and THIPWM technique is recommended for compensation of PQ disturbances and use of DC bus of DVR.

## REFERENCES

- [1] N. G. Hingorani, L. Gyugyi, and M. E. El-Hawary, *Understanding FACTS: Concepts and technology of flexible ac transmission systems*. Hoboken: Wiley, 1999, doi: 10.1109/9780470546802.

- [2] M. Eremia, C. C. Liu, and A. A. Edris, "FACTS Technologies," in *Advanced Solutions in Power Systems: HVDC, FACTS, and Artificial Intelligence*, Hoboken: Wiley, 2016, pp. 269–270, doi: 10.1002/9781119175391.part2.

- [3] P. Horowitz and W. Hill, *The art of electronics*. Cambridge: Cambridge University Press, 1989.

- [4] J. A. Houldsworth and D. A. Grant, "The Use of Harmonic Distortion to Increase the Output Voltage of a Three-Phase PWM Inverter," *IEEE Transactions on Industry Applications*, vol. IA-20, no. 5, pp. 1224–1228, Sep. 1984, doi: 10.1109/TIA.1984.4504587.

- [5] B. Singh and P. Shukla, "Control of Grid Fed PV Generation Using Infinite Impulse Response Peak Filter in Distribution Network," *IEEE Transactions on Industry Applications*, vol. 56, no. 3, pp. 3079–3089, May 2020, doi: 10.1109/TIA.2020.2968287.

- [6] V. F. Pires, A. Cordeiro, D. Foito, and J. F. Silva, "A Multilevel Converter Topology for a STATCOM System Based on Four-Leg Two-Level Inverters and Cascaded Scott Transformers," *IEEE Transactions on Power Delivery*, vol. 37, no. 3, pp. 1391–1402, Jun. 2022, doi: 10.1109/TPWRD.2021.3086399.

- [7] M. P. Thakre, P. S. Jagtap, and T. S. Barhate, "Voltage Sag Compensation of Induction Motor with 6 Pulse VSI based DVR," in *2019 International Conference on Smart Systems and Inventive Technology (ICSSIT)*, IEEE, Nov. 2019, pp. 493–498, doi: 10.1109/ICSSIT46314.2019.8987597.

- [8] A. M. Rauf and V. Khadkikar, "An Enhanced Voltage Sag Compensation Scheme for Dynamic Voltage Restorer," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 5, pp. 2683–2692, May 2015, doi: 10.1109/TIE.2014.2362096.

- [9] S. B. Q. Naqvi, S. Kumar, and B. Singh, "Three-Phase Four-Wire PV System for Grid Interconnection at Weak Grid Conditions," *IEEE Transactions on Industry Applications*, vol. 56, no. 6, pp. 7077–7087, Nov. 2020, doi: 10.1109/TIA.2020.3020931.

- [10] R. S. Kadam and M. P. Thakre, "Assessment of an Improved Voltage Flicker Remediation Treatment Method Employing VSC-Based STATCOM," in *2021 5th International Conference on Trends in Electronics and Informatics (ICOEI)*, IEEE, Jun. 2021, pp. 267–272, doi: 10.1109/ICOEI51242.2021.9452840.

- [11] K. J. Åström and B. Wittenmark, "Computer-controlled systems. Theory and design, ser. prentice-hall information and system science," Upper Saddle River, NJ: Prentice-Hall, 1997.

- [12] M. P. Thakre and N. Kumar, "Evaluation and Control Perceptive of VSM-Based Multilevel PV-STATCOM for Distributed Energy System," *Mapan - Journal of Metrology Society of India*, vol. 36, no. 3, pp. 561–578, 2021, doi: 10.1007/s12647-021-00481-x.

- [13] C. Tu, Q. Guo, F. Jiang, H. Wang, and Z. Shuai, "A Comprehensive Study to Mitigate Voltage Sags and Phase Jumps Using a Dynamic Voltage Restorer," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 2, pp. 1490–1502, Jun. 2020, doi: 10.1109/JESTPE.2019.2914308.

- [14] M. P. Thakre and A. Ahmad, "Interline Power Flow Controller (IPFC) Deployment in Long Transmission Lines and its Effects on Distance Relay," *Journal of The Institution of Engineers (India): Series B*, vol. 103, no. 2, pp. 491–505, Apr. 2022, doi: 10.1007/s40031-021-00637-y.

- [15] P. Roncero-Sánchez, E. Acha, J. E. Ortega-Calderon, V. Feliu, and A. Garcia-Cerrada, "A versatile control scheme for a dynamic voltage restorer for power-quality improvement," *IEEE Transactions on Power Delivery*, vol. 24, no. 1, pp. 277–284, 2009, doi:

10.1109/TPWRD.2008.2002967.

[16] J. G. Nielsen, M. Newman, H. Nielsen, and F. Blaabjerg, "Control and testing of a dynamic voltage restorer (DVR) at medium voltage level," *IEEE Transactions on Power Electronics*, vol. 19, no. 3, pp. 806–813, 2004, doi: 10.1109/TPEL.2004.826504.

[17] M. P. Thakre, A. Ahmad, and K. Bhadane, "Measurement Class Phasor Measurement Unit Compliance for Electrical Grid Monitoring," *MAPAN*, vol. 37, no. 1, pp. 125–135, Mar. 2022, doi: 10.1007/s12647-021-00440-6.

[18] J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," *Conference Proceedings - IEEE Applied Power Electronics Conference and Exposition - APEC*, vol. 2, pp. 1267–1273, 2001, doi: 10.1109/apec.2001.912528.

[19] H. Kim and S. K. Sul, "Compensation voltage control in dynamic voltage restorers by use of feed forward and state feedback scheme," *IEEE Transactions on Power Electronics*, vol. 20, no. 5, pp. 1169–1177, 2005, doi: 10.1109/TPEL.2005.854052.

[20] B. Panda and S. Behera, "Mitigation of voltage sag using DVR under feedback and feedforward control scheme," *International Journal of Engineering, Science and Technology*, vol. 2, no. 10, pp. 44–55, 2011, doi: 10.4314/ijest.v2i10.64011.

[21] M. J. Newman, D. G. Holmes, J. G. Nielsen, and F. Blaabjerg, "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level," *IEEE Transactions on Industry Applications*, vol. 41, no. 6, pp. 1744–1753, 2005, doi: 10.1109/TIA.2005.858212.

[22] L. J. Cheng, Z. J. Zeng, L. R. Chang-Chien, M. C. Tsai, K. V. Ling, and I. H. Wu, "Model Predictive Direct Torque Control of Permanent Magnet Synchronous Motor for Torque Ripple Reduction," in *2019 IEEE 4<sup>th</sup> International Future Energy Electronics Conference, IFEEC 2019*, IEEE, Nov. 2019, pp. 1–6, doi: 10.1109/IFEEC47410.2019.9014681.

[23] I. C. Damian and M. Eremia, "Performance Analysis of a Full Bridge Modular Multilevel Converter for High Voltage DC Transmission Using Various Pulse Width Modulation Techniques," in *2021 9<sup>th</sup> International Conference on Modern Power Systems (MPS)*, IEEE, Jun. 2021, pp. 1–5, doi: 10.1109/MPS52805.2021.9492678.

[24] C. Kumar and M. K. Mishra, "Predictive Voltage Control of Transformerless Dynamic Voltage Restorer," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 5, pp. 2693–2697, 2015, doi: 10.1109/TIE.2014.2365753.

[25] B. Jose and V. Mini, "Analysis of control strategies in transformerless dynamic voltage restorer," *2017 International Conference on Innovative Research in Electrical Sciences, IICRES 2017*, pp. 1–7, 2017, doi: 10.1109/IICRES.2017.8078293.

[26] P. Thankachen and D. A. Thomas, "Hysteresis controller based fault current interruption using DVR," *2014 Annual International Conference on Emerging Research Areas: Magnetics, Machines and Drives, AICERA/iCMM 2014 - Proceedings*, pp. 455–460, 2014, doi: 10.1109/AICERA.2014.6908241.

[27] P. Li, L. Xie, J. Han, S. Pang, and P. Li, "New Decentralized Control Scheme for a Dynamic Voltage Restorer Based on the Elliptical Trajectory Compensation," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 8, pp. 6484–6495, Aug. 2017, doi: 10.1109/TIE.2017.2682785.

[28] J. Zhang and D. Meng, "Improving Tracking Accuracy for Repetitive Learning Systems by High-Order Extended State Observers," *IEEE Transactions on Neural Networks and Learning Systems*, pp. 1–10, 2022, doi: 10.1109/TNNLS.2022.3166797.

[29] Y. Yang *et al.*, "A Novel Cascaded Repetitive Controller of an LC-Filtered H6 Voltage-Source Inverter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 11, no. 1, pp. 556–566, Feb. 2023, doi: 10.1109/JESTPE.2022.3212683.

[30] K. Zhou, K. Low, S. H. Tan, D. Wang, and Y. Qiang, "Odd-harmonic repetitive controlled CVCF PWM inverter with phase lead compensation," in *Industry Applications Conference, 2004. 39<sup>th</sup> IAS Annual Meeting.*, IEEE, pp. 177–182, doi: 10.1109/IAS.2004.1348405.

[31] M. Karimian and A. Jalilian, "Proportional-repetitive control of a dynamic voltage restorer (DVR) for power quality improvement," *2012 Proceedings of 17<sup>th</sup> Conference on Electrical Power Distribution, EPDC 2012*, pp. 1–6, 2012.

## BIOGRAPHIES OF AUTHORS

**Dr. Pawan C. Tapre**    received the B.E. and M.E. degrees in Electrical Power System Engineering from Sant Gadge Baba Amravati University (SGBAU), Maharashtra, India, in 1995 and 2002 respectively, and a Ph.D. degree in Electrical Engineering from Dr. C.V. Raman University (Dr. CVRU), Bilaspur, Chhattisgarh, India in 2022. Currently, he is an Assistant Professor at the Department of Electrical Engineering, SND College of Engineering and Research Center, Yeola (Nashik), Maharashtra, India. His research interests include deregulated power systems, flexible AC transmission systems (FACTS), power systems, and power system protection. He can be contacted at email: pawan.tapre73@gmail.com.

**Dr. Mohan P. Thakre**    received the B.Tech. and M.Tech. degrees in electrical power engineering from Dr. Babasaheb Ambedkar Technological University (Dr. BATU), Maharashtra, India, in 2009 and 2011 respectively, and the Ph.D. degree in electrical engineering from Visvesvaraya National Institute of Technology (VNIT), Nagpur, Maharashtra, India in 2017. Currently, he is an Associate Professor at the Department of Electrical Engineering, SVERI's College of Engineering, Solapur, India. His research interests include FACTS controllers, power system protection, electrical vehicles, and motor drives. He can be contacted at email: mohanthakre@gmail.com.

**Dr. Ramesh S. Pawase** received the B.E. Electronics Engineering and M.Tech. Electronics and Telecommunication Engineering from Amrutvahini College of Engineering, Sangamner and Dr. Babasaheb Ambedkar Technological University (Dr. BATU), Maharashtra, India, in 2004 and 2009 respectively, and the Ph.D. degree in Electronics and Telecommunication Engineering from Savitribai Phule Pune University, Maharashtra, India in 2019. Currently, he is an Associate Professor at the Department of Electronics and Telecommunication Engineering, Amrutvahini College of Engineering, Sangamner, India. His research interests include MEMS sensors, CMOS-ASIC, and power electronics. He can be contacted at email: rameshpawase@gmail.com.

**Mr. Jaywant S. Thorat** received the B.E.(Electrical) from Govt. College of Engineering Karad, Maharashtra, India in 1992. Presently he is appearing M.E. (Electrical Power System) from K. K. Wagh Institute of Engineering Education and Research, Nashik, Maharashtra, India. Currently he is head of Research and Development at Vision Vidyalay Engineers Private Limited. Thane, Maharashtra, India. His research interest includes medium voltage electrical equipments and electrical power distribution system. He can be contacted at email: jaywant@visionvidyalay.com.

**Dr. Dipak J. Dahigaonkar** received a Ph.D. in Electronics Engineering from SGB Amravati University. He is having 26 years of teaching and 4 years of industry experience. He has published many research papers in National and International Journals of repute. He has 4 patents, 1 book, and 3 copyrights to his credit. He is a member of professional organizations like ISTE and IE (I). His areas of interest include electronic circuits, VLSI design, smart sensing devices, and computer networks. Currently, he is also serving as Chairperson of the Interdisciplinary Board of studies, Shri Ramdeobaba College of Engineering and Management (RCOEM), and in charge of the RCOEM Media Center. He can be contacted at email: dahigaonkar@rkneu.edu.

**Dr. Rahul G. Mapari** received bachelor and master degree in Electronics Engineering from Savitribai Phule Pune University, India in 2004 and 2007 respectively and a PhD degree in Electronics and Telecommunication engineering from Amravati University, India in 2016. From 2005 to 2015 he worked at Savitribai Phule Pune University involved in teaching and research in power converters. Since 2017, he has been in the Department of Electronics and Telecommunication Engineering, Pimpri Chinchwad College of Engineering and Research and is currently working as a Professor and Head of the Department. His research interest is power converters and power electronics. He can be contacted at email: rahul.mapari@pccoe.in.

**Dr. Sunil Somnath Kadlag** received B.E in Electrical Engineering from Dr. Babasaheb Ambedkar Marathwada University, Aurangabad (Dr B.A.M.U) in 1997 and M.E in Electrical Engineering (Control System) from Government College of Engineering Pune (Pune University) in 2005 and Ph.D. in Electrical Engineering from Suresh Gyan Vihar University Jaipur (Rajasthan) in 2021. His research area is electric vehicles. He is presently working as an Associate Professor and Head, of the Department of Electrical Engineering, Amrutvahini College of Engineering, Sangamner, Savitribai Phule Pune University, Pune, Maharashtra, India. He can be contacted at email: sunilkadlag5675@gmail.com.

**Dr. Shridhar Khule** obtained Ph.D. degree in Electrical Engineering specializing in power systems from Sant Gadge Baba Amravati University, Amravati, Maharashtra, India in 2021. He occupied various positions to serve engineering institutes for about 20 years. He is currently working as Professor in the Department of Electrical Engineering, Matoshri College of Engineering and Research Center, Nashik. His research interests power system. He attended International and National conferences. He is a member of professional bodies such as ISTE and IET. He can be contacted at email: shridhar.khule@matoshri.edu.in.